在單片機應用系統的設計與開發過程中,電磁干擾是一個普遍存在且嚴重影響系統穩定性與可靠性的問題。干擾可能導致程序跑飛、數據錯誤、控制失靈甚至硬件損壞。因此,識別干擾源并采取有效的抑制措施,是保障電子系統穩健運行的關鍵。本文將系統性地探討單片機設計過程中電磁干擾的主要來源,并提供一系列從原理到實踐的綜合性抗干擾策略。

一、電磁干擾的主要來源

電磁干擾通常分為系統內部干擾和外部環境干擾兩大類。

- 內部干擾:

- 電源噪聲:開關電源的紋波、數字電路快速開關引起的電流突變,通過電源內阻和走線耦合到單片機及其外圍電路。

- 信號串擾:PCB上高速或大電流信號線(如時鐘線、PWM輸出線)通過寄生電容和互感,對鄰近的敏感模擬信號線(如傳感器輸入、ADC參考電壓)產生耦合干擾。

- 地線噪聲:地線設計不當(如單點接地未做好、地線回路面積過大)導致地電位在系統不同點存在波動,形成“地彈”,嚴重影響模擬電路和數字接口的基準。

- 元器件輻射:單片機本身、晶體振蕩器、高速邏輯器件、繼電器、電機驅動電路等都是潛在的輻射源。

- 外部干擾:

- 空間輻射干擾:來自其他設備的無線電發射、靜電放電、雷擊感應等。

- 傳導干擾:通過電源線、信號電纜等導線耦合進入系統的干擾,如電網波動、其他設備的開關噪聲。

二、硬件層面的抗干擾設計策略

硬件設計是構建抗干擾能力的第一道,也是最重要的防線。

- 優化電源設計:

- 電源去耦與濾波:在每塊集成電路(尤其是單片機、FPGA、驅動芯片)的電源引腳附近,緊貼器件放置一個0.1μF的陶瓷電容(用于濾除高頻噪聲),并可能在電源入口處并聯一個10-100μF的電解或鉭電容(用于抑制低頻紋波)。

- 使用線性穩壓器(LDO):對模擬電路、ADC參考源等敏感部分,采用噪聲特性好的LDO進行獨立供電,并與數字電源進行隔離。

- 電源入口防護:加入共模電感、TVS管、壓敏電阻等元件,抑制從電網傳入的浪涌和脈沖群干擾。

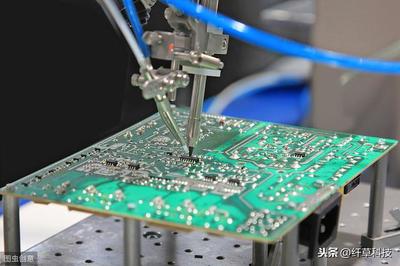

- 科學的PCB布局與布線:

- 分區與分層:將數字電路區、模擬電路區、大功率驅動區進行物理隔離。采用多層板(至少4層),設置完整的電源層和接地層,為信號提供低阻抗的返回路徑,并起到屏蔽作用。

- 關鍵信號線處理:時鐘線、復位線等關鍵信號線應盡量短、粗,并用地線包絡或走在內層進行屏蔽。敏感模擬信號線應遠離噪聲源,必要時采用差分走線。

- 最小化回路面積:信號線與其回流地線構成的環路面積越小,對外輻射和接收干擾的能力就越弱。保持電源和地線緊密耦合。

- 接地系統設計:根據電路類型采用混合接地策略。高頻數字電路宜采用多點接地以降低地線阻抗;低頻模擬電路宜采用單點接地以避免地環路;兩者之間通過磁珠或0歐電阻在一點連接。確保接地路徑低阻抗、低感抗。

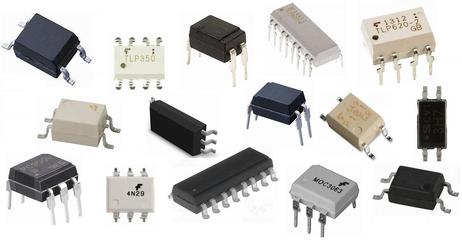

- 接口與外圍電路防護:

- I/O口隔離與緩沖:對連接長線或外部設備的I/O口,使用光耦、數字隔離芯片或緩沖器(如74HC245)進行隔離,防止干擾侵入核心電路。

- 信號濾波:在模擬信號輸入ADC前,加入RC低通濾波器,截止頻率略高于有用信號頻率,以抑制高頻噪聲。對數字輸入信號,可使用施密特觸發器整形并配合小電容濾波。

- 屏蔽與接地:對特別敏感或輻射強的部分,使用金屬屏蔽罩。所有屏蔽體必須良好接地。

三、軟件層面的抗干擾加固

當硬件措施無法完全消除干擾時,軟件層面的容錯設計是最后的安全網。

- 程序穩健性設計:

- 指令冗余與軟件陷阱:在關鍵跳轉指令(如JMP, CALL)前插入幾條NOP指令,并在程序存儲器的未使用區域填充軟件陷阱(如跳轉到系統復位或錯誤處理程序的指令),以防止程序跑飛后無法恢復。

- 看門狗定時器:必須啟用并正確喂狗。看門狗能在程序失控后強制系統復位,是應對死機和程序跑飛的最有效手段之一。

- 數據校驗與備份:對重要的配置參數、累計數據等,采用多副本存儲(如EEPROM中的三個區域),并配合CRC或求和校驗,定期檢查與修復。

- 輸入信號的數字濾波:

- 多次采樣與中值/均值濾波:對開關量輸入進行多次延時采樣(如每隔1ms采樣一次,連續5次結果一致才確認),防止毛刺干擾。對模擬量進行軟件濾波,如中值濾波、滑動平均濾波等。

- 輸出狀態的保護與恢復:

- 周期性地刷新輸出端口的狀態,特別是在執行完一段可能不穩定的代碼之后,確保輸出不受干擾影響。對于重要的控制輸出,可以設計“安全狀態”,在系統異常時能自動切換到該狀態。

四、系統級與測試驗證

- 整機屏蔽與接地:整個設備機箱應作為屏蔽體,并確保其與安全地或信號地良好連接。所有進出線纜應通過濾波器或屏蔽接頭連接。

- 標準符合性測試:在設計后期,應依據相關行業標準(如IEC 61000系列)進行電磁兼容性測試,包括靜電放電、電快速瞬變脈沖群、浪涌、輻射發射與抗擾度等,根據測試結果進行針對性的改進。

###

擺脫電磁干擾是一個貫穿單片機系統設計始終的系統工程,需要從干擾源、傳播路徑和敏感設備三個環節協同治理。優秀的抗干擾設計源于對電路原理的深刻理解、嚴謹的工程實踐以及大量的測試驗證。通過將上述硬件布局、軟件策略與系統防護有機結合,設計師能夠顯著提升單片機系統的電磁兼容性,確保其在復雜的電磁環境中穩定、可靠地運行。